#### **Features**

- 2.5V to 5.5V Input Voltage Range

- Fixed 1.25V Output Voltage

- 1A Continuous Output Current

- 1.5MHz Switching Frequency

- Built-in Short Protection

- Built-in Over Current Limit

- Built-in Over Voltage Protection

- PFM Mode for High Efficiency in Light Load

- High Efficiency: Up to 96%

- Internal Soft-Start

- No Schottky Diode Required

- No Resistor Divider Required

- Over Temperature Protected

- Low Shutdown Current: 0.1µA Typ.

- Available in SOT23-5/SON763 package

- -40°C to +85°C Temperature Range

## **Applications**

True Wireless Stereo

Other Applications

## **General Description**

The RY8001 is a high-efficiency monolithic synchronous buck regulator using a constant frequency, current mode architecture. The device is available in fixed 1.25V output voltage. Supply current drops to 0.1uA in shutdown mode. The 2.5V to 5.5V input voltage range makes the RY8001 ideally suited for single Li-Ion battery powered applications. PWM/PFM mode operation provides very low output ripple voltage for noise sensitive applications. Switching frequency is internally set at 1.5MHz, allowing the use of small surface mount inductors and capacitors. The RY8001 requires a minimal number of readily available, external components and is available in a space saving SOT23-5 and SON763 package.

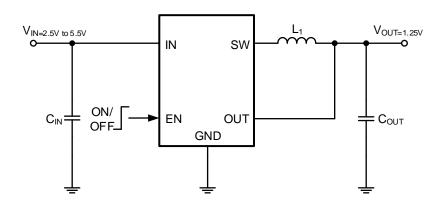

# **Typical Application Circuit**

**Basic Application Circuit**

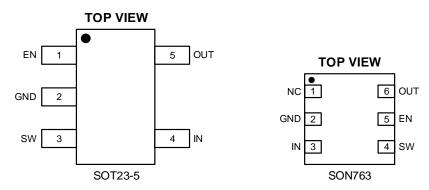

# **Pin Description**

## **Pin Configuration**

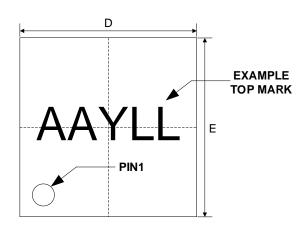

RY8001-1CT5 Top Marking: Ay<u>YLL</u> (device code: Ay, Y=year code, LL= lot number code) RY8001-1CS6 Top Marking: Az<u>YLL</u> (device code: Az, Y=year code, LL= lot number code)

#### **Pin Description**

| Pin | SOT23-5 | SON763 | Function                                                                                                                                                      |

|-----|---------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EN  | 1       | 5      | Chip Enable Pin. Drive EN above 1.2V to turn on the part. Drive EN below 0.6V to turn it off. Do not leave EN floating.                                       |

| GND | 2       | 2      | Ground Pin                                                                                                                                                    |

| SW  | 3       | 4      | Power Switch Output. It is the switch node connection to Inductor. This pin connects to the drains of the internal P-ch and N-ch MOSFET switches.             |

| IN  | 4       | 3      | Power Supply Input. Must be closely decoupled to GND with a 10µF or greater ceramic capacitor.                                                                |

| OUT | 5       | 6      | Output Voltage Power Rail and Input Sense Pin for Output Voltage. Connect load to this pin. Output capacitor is needed to decrease the output voltage ripple. |

| NC  | /       | 1      | Not Connected                                                                                                                                                 |

# **Order Information** (1)

| Marking       | Part No. |             | Description                                                                             | Package | T/R Qty. |

|---------------|----------|-------------|-----------------------------------------------------------------------------------------|---------|----------|

| Ay <u>YLL</u> | 70301075 |             | RY8001-1CT5 Buck, V <sub>IN</sub> 2.5-5.5V, V <sub>OUT</sub> 1.25V, 1A, 1.5MHz, SOT23-5 |         | 3000PCS  |

| Az <u>YLL</u> | 70301076 | RY8001-1CS6 | RY8001-1CS6 Buck, V <sub>IN</sub> 2.5-5.5V, V <sub>OUT</sub> 1.25V, 1A, 1.5MHz, SON763  | SON763  | 3000PCS  |

Note (1): All RYCHIP parts are Pb-Free and adhere to the RoHS directive.

## **Specifications**

## Absolute Maximum Ratings (1) (2)

| Item                                           | Min             | Max                   | Unit |

|------------------------------------------------|-----------------|-----------------------|------|

| V <sub>IN</sub> voltage                        | -0.3            | 6                     | V    |

| EN voltage                                     | -0.3            | 6                     | V    |

| SW voltage                                     | -0.3            | V <sub>IN</sub> +0.5V | V    |

| OUT Voltage                                    | -0.3            | 6                     | V    |

| Power dissipation (3)                          | Internally Limi | ited                  |      |

| Operating junction temperature, T <sub>J</sub> | -40             | 150                   | °C   |

| Storage temperature, T <sub>stg</sub>          | -55             | 150                   | °C   |

| Lead Temperature (Soldering, 10sec.)           |                 | 260                   | °C   |

Note (1): Exceeding these ratings may damage the device.

Note (2): The device is not guaranteed to function outside of its operating conditions.

Note (3): The maximum allowable power dissipation is a function of the maximum junction temperature,  $T_{J(MAX)}$ , the junction-to-ambient thermal resistance,  $R_{\theta JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any ambient temperature is calculated using:  $P_{D(MAX)} = (T_{J(MAX)} - T_A)/R_{\theta JA}$ . Exceeding the maximum allowable power dissipation causes excessive die temperature, and the regulator goes into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J = 160$ °C (typical) and disengages at  $T_J = 130$ °C (typical).

## **ESD Ratings**

| Item                   | Description                          | Value | Unit |

|------------------------|--------------------------------------|-------|------|

|                        | Human Body Model (HBM)               |       |      |

| V <sub>(ESD-HBM)</sub> | ANSI/ESDA/JEDEC JS-001-2014          | ±2000 | V    |

|                        | Classification, Class: 2             |       |      |

|                        | Charged Device Mode (CDM)            |       |      |

| V <sub>(ESD-CDM)</sub> | ANSI/ESDA/JEDEC JS-002-2014          | ±200  | V    |

|                        | Classification, Class: C0b           |       |      |

| Т                      | JEDEC STANDARD NO.78E APRIL 2016     | +150  | 4    |

| ILATCH-UP              | Temperature Classification, Class: I | ±150  | mA   |

## **Recommended Operating Conditions**

| Item                               | Min | Max | Unit |

|------------------------------------|-----|-----|------|

| Operating junction temperature (1) | -40 | 125 | °C   |

| Operating temperature range        | -40 | 85  | °C   |

| Input voltage V <sub>IN</sub>      | 2.5 | 5.5 | V    |

| Output current                     | 0   | 1   | A    |

Note (1): All limits specified at room temperature (TA = 25°C) unless otherwise specified. All room temperature limits are 100% production tested. All limits at temperature extremes are ensured through correlation using standard Statistical Quality Control (SQC) methods. All limits are used to calculate Average Outgoing Quality Level (AOQL).

#### **Thermal Information**

| Item                 | Description                                   | SOT23-5 | SON763 | Unit |

|----------------------|-----------------------------------------------|---------|--------|------|

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance (1)(2) | 180     | 95     | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance     | 130     | 49.5   | °C/W |

| $R_{	heta JB}$       | Junction-to-board thermal resistance          | 45      | 15.5   | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter    | 35      | 3.2    | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter  | 45      | 15.5   | °C/W |

Note (1): The package thermal impedance is calculated in accordance to JESD 51-7.

Note (2): Thermal Resistances were simulated on a 4-layer, JEDEC board

# Electrical Characteristics (1)(2)

V<sub>IN</sub>=5V, T<sub>A</sub>=25°C, unless otherwise specified.

| Parameter                         | Conditions                         | Min. | Тур. | Max. | Unit |

|-----------------------------------|------------------------------------|------|------|------|------|

| Input Voltage Range               |                                    | 2.5  |      | 5.5  | V    |

| Output Voltage                    |                                    |      | 1.25 |      | V    |

| Supply Current (Quiescent)        | $V_{\rm EN} = 3.0 \mathrm{V}$      |      | 40   |      | μΑ   |

| Supply Current (Shutdown)         | $V_{EN} = 0$ or $EN = GND$         |      | 0.1  |      | μΑ   |

| High-Side Switch On-Resistance    | I <sub>SW</sub> =100mA             |      | 300  |      | mΩ   |

| Low-Side Switch On-Resistance     | I <sub>SW</sub> =-100mA            |      | 200  |      | mΩ   |

| Upper Switch Current Limit        |                                    | 1.5  |      |      | A    |

| Over Voltage Protection Threshold |                                    |      | 6    |      | V    |

| Switching Frequency               |                                    |      | 1.5  |      | MHz  |

| EN Rising Threshold               |                                    | 1.2  |      |      | V    |

| EN Falling Threshold              |                                    |      |      | 0.6  | V    |

| EN Threshold Hysteresis           |                                    |      | 100  |      | mV   |

|                                   | Wake up V <sub>IN</sub> Voltage    |      | 2.3  | 2.45 | V    |

| Under-Voltage Lockout Threshold   | Shutdown V <sub>IN</sub> Voltage   | 1.75 | 1.9  |      | V    |

|                                   | Hysteresis V <sub>IN</sub> voltage |      | 400  |      | mV   |

| Soft Start                        |                                    |      | 1    |      | mS   |

| Thermal Shutdown                  |                                    |      | 160  |      | °C   |

| Thermal Hysteresis                |                                    |      | 30   |      | °C   |

Note (1): MOSFET on-resistance specifications are guaranteed by correlation to wafer level measurements.

Note (2): Thermal shutdown specifications are guaranteed by correlation to the design and characteristics analysis.

## **Functions Description**

#### **Internal Regulator**

The RY8001 is a current mode step down DC/DC converter that provides excellent transient response with no extra external compensation components. This device contains an internal, low resistance, high voltage power MOSFET, and operates at a high 1.5MHz operating frequency to ensure a compact, high efficiency design with excellent AC and DC performance.

### **Under-Voltage Lockout (UVLO)**

Under-voltage lockout (UVLO) protects the chip from operating at an insufficient supply voltage. UVLO protection monitors the internal regulator voltage. When the voltage is lower than UVLO threshold voltage, the device is shut off. When the voltage is higher than UVLO threshold voltage, the device is enabled again.

#### **Thermal Shutdown**

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. When the silicon die temperature exceeds 160°C, it shuts down the whole chip. When the temperature falls below its lower threshold (Typ. 130°C) the chip is enabled again.

#### **Internal Soft-Start**

The device has a built-in soft start that ramps up the output voltage at a controlled slew rate to avoid overshoot at startup. The soft start time is about 1ms typically.

#### Startup and Shutdown

If both  $V_{IN}$  and EN are higher than their appropriate thresholds, the chip starts. The reference block starts first, generating stable reference voltage and currents, and then the internal regulator is enabled. The regulator provides stable supply for the remaining circuitries. Three events can shut down the chip: EN low, VIN low and thermal shutdown. In the shutdown procedure, the signaling path is first blocked to avoid any fault triggering. The comp voltage and the internal supply rail are then pulled down. The floating driver is not subject to this shutdown command.

## **Applications Information**

#### Selecting the Inductor

The recommended inductor values are shown in the Application Diagram. It is important to guarantee the inductor core does not saturate during any foreseeable operational situation. The inductor should be rated to handle the maximum inductor peak current: Care should be taken when reviewing the different saturation current ratings that are specified by different manufacturers. Saturation current ratings are typically specified at 25°C, so ratings at maximum ambient temperature of the application should be requested from the manufacturer. The inductor value can be calculated with:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_L \times F_{OSC}}$$

Where  $\Delta I_L$  is the inductor ripple current. Choose inductor ripple current to be approximately 30% to 40% of the maximum load current. The maximum inductor peak current can be estimated as:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_L}{2}$$

Under light load conditions below 100mA, larger inductance is recommended for improved efficiency. Larger inductances lead to smaller ripple currents and voltages, but they also have larger physical dimensions, lower saturation currents and higher linear impedance. Therefore, the choice of inductance should be compromised according to the specific application.

#### Selecting the Input Capacitor

The input current to the step-down converter is discontinuous and therefore requires a capacitor to supply AC current to the step-down converter while maintaining the DC input voltage. For a better performance, use ceramic capacitors placed as close to VIN as possible and a  $0.1\mu F$  input capacitor to filter out high frequency interference is recommended. Capacitors with X5R and X7R ceramic dielectrics are recommended because they are stable with temperature fluctuations.

The capacitors must also have a ripple current rating greater than the maximum input ripple current of the converter. The input ripple current can be estimated with Equation:

$$I_{CIN} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}$$

From the above equation, it can be concluded that the input ripple current reaches its maximum at  $V_{IN}=2V_{OUT}$  where  $I_{CIN}=\frac{I_{OUT}}{2}$ . For simplification, choose an input capacitor with an RMS current rating greater than half of the maximum load current.

The input capacitance value determines the input voltage ripple of the converter. If there is an input voltage ripple requirement in the system, choose the input capacitor that meets the specification. The input voltage ripple can be estimate with Equation:

$$\Delta V_{IN} = \frac{I_{OUT}}{F_{OSC} \times C_{IN}} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

Similarly, when  $V_{IN}=2V_{OUT}$ , input voltage ripple reaches its maximum of  $\Delta V_{IN}=\frac{1}{4}\times\frac{I_{OUT}}{F_{OSC}\times C_{IN}}$ .

### **Selecting the Output Capacitor**

An output capacitor is required to maintain the DC output voltage. The output voltage ripple can be estimated with Equation:

$$\Delta V_{OUT} = \frac{V_{OUT}}{F_{OSC} \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times \left(R_{ESR} + \frac{1}{8 \times F_{OSC} \times C_{OUT}}\right)$$

There are some differences between different types of capacitors. In the case of ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance. The output voltage ripple is mainly caused by the capacitance. For simplification, the output voltage ripple can be estimated with Equation:

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 \times F_{OSC}^2 \times L \times C_{OUT}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

A larger output capacitor can achieve a better load transient response, but the maximum output capacitor limitation should also be considered in the design application. If the output capacitor value is too high, the output voltage will not be able to reach the design value during the soft-start time and will fail to regulate. The maximum output capacitor value ( $C_{OUT\ MAX}$ ) can be limited approximately with Equation:

$$C_{OUT\_MAX} = (I_{LIM\_AVG} - I_{OUT}) \times T_{SS}/V_{OUT}$$

Where L<sub>LIM\_AVG</sub> is the average start-up current during the soft-start period, and T<sub>SS</sub> is the soft-start time.

On the other hand, special attention should be paid when selecting these components. The DC bias of these capacitors can result in a capacitance value that falls below the minimum value given in the recommended capacitor specifications table.

The ceramic capacitor's actual capacitance can vary with temperature. The capacitor type X7R, which operates over a temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C, will only vary the capacitance to within  $\pm15\%$ . The capacitor type X5R has a similar tolerance over a reduced temperature range of  $-55^{\circ}$ C to  $+85^{\circ}$ C. Many large value ceramic capacitors, larger than 1uF are manufactured with Z5U or Y5V temperature characteristics. Their capacitance can drop by more than 50% as the temperature varies from 25°C to 85°C. Therefore, X5R or X7R is recommended over Z5U and Y5V in applications where the ambient temperature will change significantly above or below 25°C.

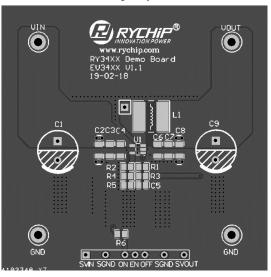

### **PC Board Layout Consideration**

PCB layout is very important to achieve stable operation. It is highly recommended to duplicate EVB layout for optimum performance. If change is necessary, please follow these guidelines for reference.

- 1. Keep the path of switching current short and minimize the loop area formed by Input capacitor, high-side MOSFET and low-side MOSFET.

- 2. Bypass ceramic capacitors are suggested to be put close to the  $V_{\rm IN}$  Pin.

- 3. Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close to the chip as possible.

- 4. V<sub>OUT</sub>, SW away from sensitive analog areas such as FB.

Connect IN, SW, and especially GND respectively to a large copper area to cool the chip to improve thermal performance and long-term reliability.

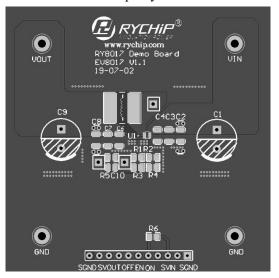

Top Layer

Bottom Layer

SOT23-5 Sample Board Layout

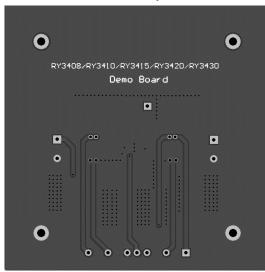

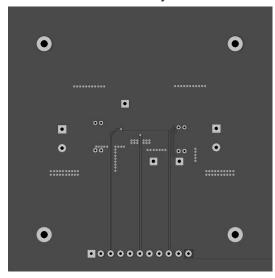

Top Layer

Bottom Layer

SON763 Sample Board Layout

## **Package Description**

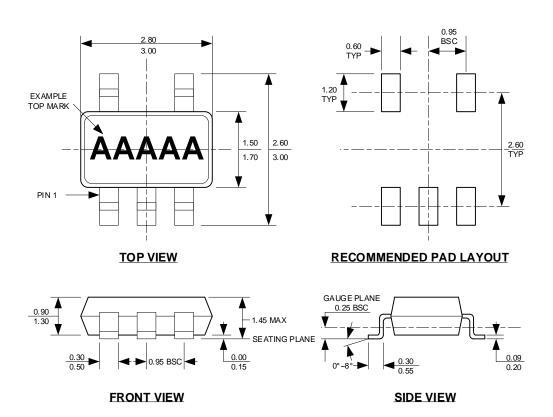

#### SOT23-5

- NOTE:

1. CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

2. PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

3. PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

4. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5. DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA.

6. DRAWING IS NOT TO SCALE.

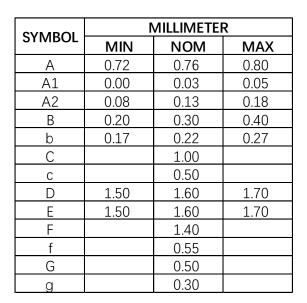

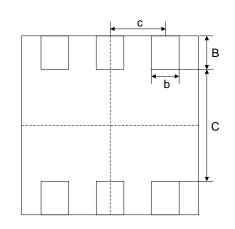

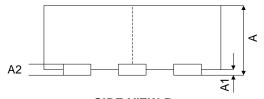

#### SON763 (1.6mm×1.6mm)

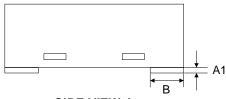

**SIDE VIEW A**

**BOTTOM VIEW**

**SIDE VIEW B**

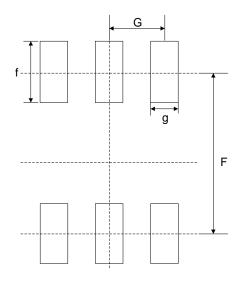

**RECOMMENDED LAND PATTERN**

- 1. CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2. PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3. PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

4. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5. DRAWING CONFORMS TO JEDEC MS-012, VARIATION BA.

- 6. DRAWING IS NOT TO SCALE.